Ultrahigh-definition (UHD) televisions, also known as 4K or Quad HD TVs, have four times the resolution of today’s HD TVs. This jump up in pixels requires a new video-coding standard, known as high-efficiency video coding, or HEVC, and researchers at the Massachusetts Institute of Technology (MIT) have developed such an HEVC chip. Though this research is not aimed at the commercial market, the challenge of implementing HEVC algorithms in silicon could helps illustrate design principles that could be broadly useful in the real world.

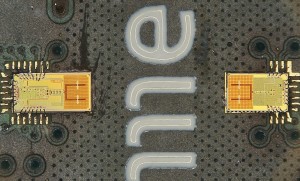

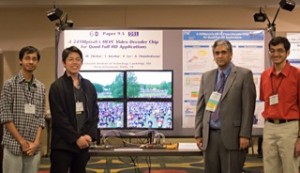

The developers of the new MIT chip see their pivotal innovation in understanding how HEVC is more complex than previous video coding standards, such as H.264/AVC, and developing an efficient hardware implementation for it. “We identified and exploited certain features in the HEVC algorithms for savings in the logic and memory areas,” says Mehul Tikekar, an MIT graduate student in electrical engineering and computer science and lead author of the paper.

Because MIT developed its “scholastic” chip at the same time the standards committee Joint Collaborative Team on Video Coding (JCT-VC) developed HEVC, the MIT researchers “were able to provide feedback to JCTVC on the complexity of their Inverse Transform algorithms, providing insight into what would help an efficient hardware implementation,” Tikekar says.

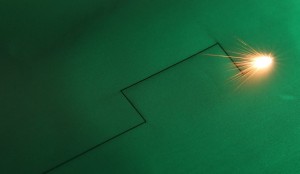

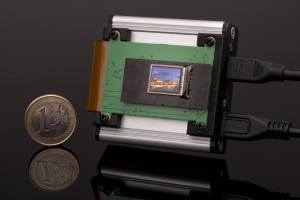

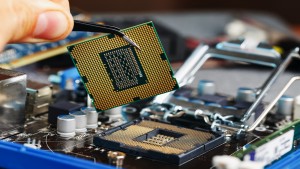

The chip, manufactured by the Taiwan Semiconductor Manufacturing Corporation, “is connected to a Xilinx FPGA which in turn talks to a DDR3 SDRAM,” Tikekar describes the design. “The DDR3 memory stores the compressed video,

called bitstream, which is input to the chip as well as decoded video output from the chip. The chip begins by decompressing the bitstream into syntax elements through a process called Entropy Decoding. The syntax elements contain motion vectors, which are used by a Motion Compensation circuit to create predicted pixels. Some corrective information, called residue is extracted from the syntax elements using Inverse Transform. The residue and predicted pixels are added, filtered and finally output as the decoded video.”

One important advance of HEVC over older video coding is the size of pixel blocks used in the processing. “HEVC can use up to 16 times larger pixel blocks than H.264/AVC and also use a large variety of smaller blocks,” Tikekar explains. His team developed techniques to handle the maximum size as well as the diversity of smaller sizes. “By efficiently pipelining the processing, we could reduce the amount of memory required to store the large blocks. We also observed key features in Inverse Transform and Motion Compensation that help reduce logic area for these processing blocks.” Furthermore, to help reduce DDR3 power consumption, they developed a more efficient way to store video data in the DDR3 memory, storing them in blocks rather than lines.

Next, Tikekar and his colleagues want to explore other application spaces for HEVC, such as 3-D TVs. “Each have their own set of challenges, such as ultra-low power consumption on mobiles and new processing techniques for 3-D,” he says in conclusion.

Written by Sandra Henderson, Research Editor, Novus Light Technologies Today.

Back to Features

Back to Features